By: Karlyn Cynthia FM, Research Student at CCRI, Asia University, Taiwan

Abstract

In VLSI systems, digital adder architectures are the most necessary components which affects the power consumption, propagation delay and area usage. This article concentrates with the comparison of four adder architectures such as Ripple Carry Adder (RCA), Carry Lookahead Adder (CLA), Carry Skip Adder (CSKA) and Carry Select Adder (CSLA). Ripple Carry Adder is quite simple architecture but it is slow, Carry Lookahead Adder has faster operation but requires more hardware and it is a bit complex, whereas Carry Skip and Carry Select adders delivers a balanced operation between the speed and the hardware. Overall, this comparison is achieved in choosing the best or suitable architectures for high-performance VLSI designs.

Introduction

Addition is one of the common operations in digital systems which includes processors and embedded applications. The performance of these systems is dependent on the ability of the adder architecture which has been used. Various adder architectures handles carry propagation in a different way which leads to the deviations in speed, power and area [3]. Thus, a comparative analysis of all the digital adder architectures is required to understand their trade-offs in order to identify the suitable design for high-performance VLSI applications.

Overview of Adder Architectures

Ripple Carry Adder (RCA)

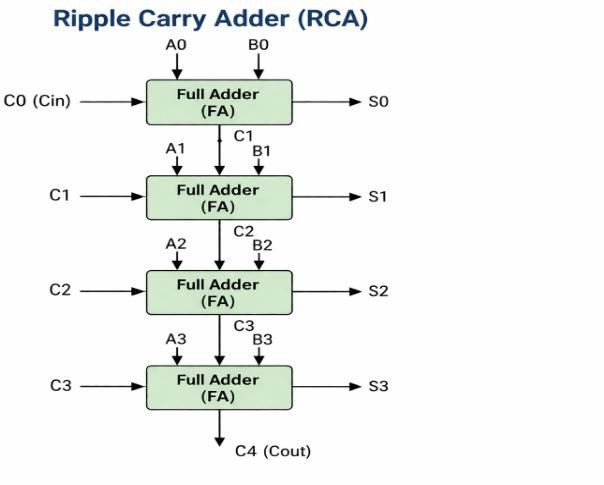

This adder architecture is quite simple one where the carry output propagates in a continuous manner from one stage to the other. This leads to the increase in delay as the number of bits increases. It also requires less hardware usage and it is easy to implement as its high delay makes it improper for high-speed VLSI applications as shown in figure 1[3].

Figure 1: Ripple Carry Adder where carry moves step by step from one stage to the next.

Carry Lookahead Adder (CLA)

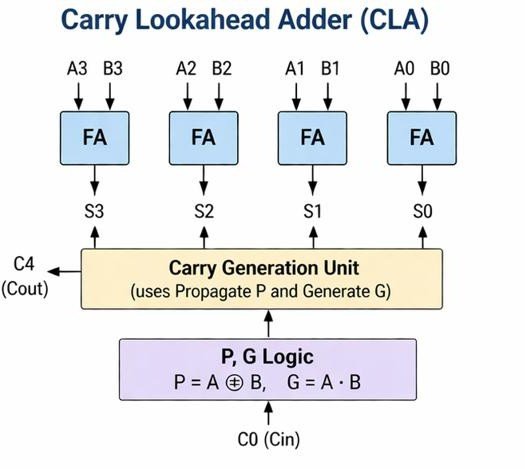

The is a high-speed adder architecture which improves the overall performance by decreasing the carry propagation delay. It calculates the carry signals in prior, making the performance of the circuit faster mainly for larger bit widths, as illustrated in figure 2. This adder also improves the speed by increasing the complexity, area and power consumption [5][8].

Figure 2: Carry Lookahead Adder where carry is calculated in advance to make addition faster.

Carry Skip Adder (CSKA)

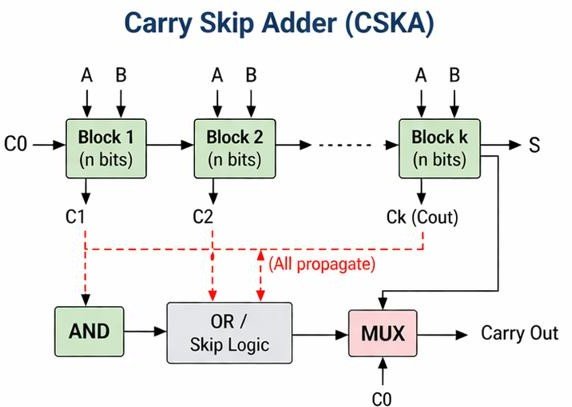

This adder groups all the full adders into blocks in order to improve the performance of the circuit. This allows the carry to skip certain blocks by using the skip logic, which reduces delay. It also decreases the carry propagation time which is compared to the Ripple Carry Adders. This adder gives a balanced trade-off among area, speed and power and hardware complexity as shown in figure 3[4].

Figure 3: Carry Skip Adder where carry skips some stages to reduce delay.

Carry Select Adder (CSLA)

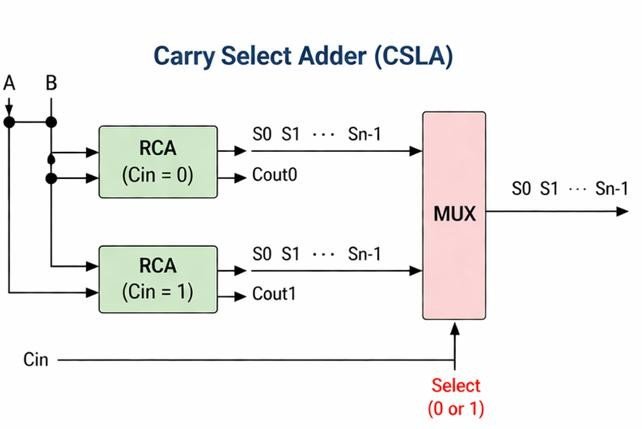

The Carry Select Adder is a high-speed adder which reduces the propagation delay by calculating the results in parallel way for Cin=0 and Cin=1. A multiplexer has been used here to select the actual output which is based on the actual carry input. This improves the speed of the circuit, but the usage of hardware is increased, as shown in figure 4.

Figure 4: Carry Select Adder where it calculates two results at the same time and selects the correct one.

Comparative Analysis

This comparison highlights the trade-offs among the delay, power and area in various adder architectures. The Ripple Carry Adder is a bit slow process due to continuous carry propagation, while the Carry Lookahead Adder is a fast process as it precomputes the carry in parallel [2][3]. The Carry Skip and Carry Select Adders gives a better balance among the performance metrics where Carry Skip Adder reduces the delay through skipping the stages and Carry Select Adder uses parallel calculation at the cost of high hardware usage [3]. A summary of this comparison is shown in table 1.

Adder | Speed | Hardware |

Ripple Carry Adder | Slow | Low |

Carry Lookahead Adder | Fast | High |

Carry Skip Adder | Medium | Medium |

Carry Select Adder | Fast | High |

Table 1: This table shows a simple comparison of different adders based on their speed and hardware needs.

Conclusion

This study compares various adder architectures which is based on propagation delay, power consumption and area usage. Ripple Carry Adder provides simple architecture, Carry Lookahead Adder is faster, Carry Skip and Carry Select Adders provide a balanced performance. Hybrid adders improve the performance by integrating the advantages of multiple designs [7][10].

References

- K. R. Rekha and S. M. Prasad, “Reconfigurable Adder Architectures for Low Power Applications,” International Journal of Engineering Research and Technology, vol. 3, no. 5, pp. 1–5, 2014.

- M. K. Verma, S. K. Singh, and R. K. Sharma, “Performance Analysis of Classified Binary Adder Architectures,” Electrica Journal, vol. 18, no. 2, pp. 120–128, 2018.

- A. Kumar and B. Singh, “Comparative Analysis of 4-bit Adder Architectures for Enhanced Efficiency in CMOS Technology,” International Journal of VLSI Design, vol. 10, no. 3, pp. 45–52, 2019.

- S. Gupta and P. Mehta, “Design of High-Speed Carry Skip Adder,” International Journal of Scientific Development and Research, vol. 3, no. 4, pp. 210–214, 2018.

- R. Patel and N. Shah, “Performance Comparison of Synchronous Adders (RCA, CLA, CSLA),” arXiv preprint arXiv:1810.01115, 2018.

- B. Ramkumar and H. M. Kittur, “Low Power and Area Efficient Carry Select Adder,” IEEE Transactions on Circuits and Systems, vol. 59, no. 6, pp. 1219–1223, 2012.

- Y. Kim and L. S. Kim, “Hybrid Carry Select Adder Using RCA and CLA,” Engineering Reports, vol. 6, no. 2, pp. 1–10, 2024.

- M. Ali, et al., “Energy Efficient Adder Architectures for High Performance Systems,” Computers, Materials & Continua, vol. 70, no. 2, pp. 1235–1250, 2022.

- “Carry Lookahead Adder,” Wikipedia. [Online]. Available: https://en.wikipedia.org/wiki/Carry-lookahead_adder. [Accessed: Apr. 2026].

- “Parallel Prefix Adders (Brent-Kung Adder),” Wikipedia. [Online]. Available: https://en.wikipedia.org/wiki/Brent–Kung_adder. [Accessed: Apr. 2026].

Cite As

Karlyn FM C, (2026) Comparative Analysis of Digital Adder Architectures for High-Speed VLSI Applications, Insights2Techinfo, pp.1