By: Karlyn Cynthia FM, Research Student at CCRI, Asia University, Taiwan

Abstract

In VLSI, Digital circuit design needs repeated calculation of performance parameters like power consumption, propagation delay and area usage. Common techniques depend on repeated synthesis, increasing the design cost and time. This article talks about a structured approach which transform the hardware designs into machine learning datasets, improving the predictive model of the performance metrics. The expected idea combines the Verilog design, synthesis by using Vivado, generation of the dataset and the machine learning approaches which follows security analysis based on dynamic power. This structure minimizes the repeated synthesis which is dependent and it provides the understanding of both performance and security of digital adder architectures.

Introduction

The primary building block in VLSI systems include digital adders which are mostly used in processors, digital signal processing units and embedded systems. The key parameters such as power consumption, delay and area are determined by the efficiency of the system [1].

Many numbers of iterations of hardware synthesis and simulation is needed to calculate these parameters. When observing different architectures and bit-widths, this process is efficient, time saving and computationally costly. New developments in machine learning have implemented these parameters without the performance of repeated synthesis [2].

This work analyses a systematic conversion of hardware designs into framed datasets which can be used to train the machine learning models. Opposite to traditional techniques, this approach combines the performance with security analysis, which makes the design more efficient and to be cautious about the security.

Problem Statement

Traditional VLSI design methods depend on repeated synthesis in order to correct the performance parameters which leads to enhanced design time and cost. In addition to this, most of the techniques concentrate only on performance evaluation and do not deal with the security concerns like vulnerability to side-channel attacks.

Even if machine learning is applied in electronic design automation, many of the research concentrate only on high-level predictions without even clearly defining how the hardware designs can be transformed into framed datasets [3]. Moreover, most of the existing works generally lose combination among the performance and security level analysis.

Accordingly, there is necessary for a consolidated structure that:

- Transforms hardware designs into machine learning datasets.

- Prediction of performance parameters effectively.

- Integrates security analysis which is based on dynamic power behaviour.

Hardware to Dataset Conversion Structure

In VLSI systems, the transformation of the hardware designs into a framed datasets allows data-driven analysis. The key parameters such as power, delay and area are taken when the digital circuits are converted into numerical model from the synthesized designs. This framework acts as the input for machine learning models to implement efficient performance prediction.

Hardware design by using Verilog HDL

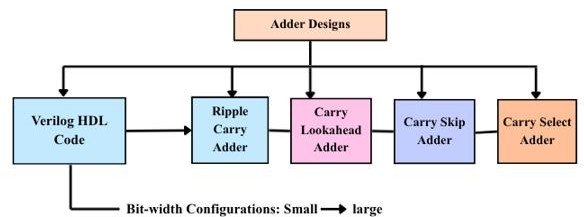

The very first stage requires designing of the digital adder architectures by using Verilog HDL (Hardware Description Language). In recently developed VLSI systems, the Register Transistor Level (RTL) design creates the base for the performance calculation which is commonly used for early-stage research [2]. Each digital adder is being implemented for multiple bit-widths in order to provide scalability and variance in the dataset. The hardware design flow using Verilog HDL is illustrated in Fig. 1.

Figure 1: Verilog based hardware design

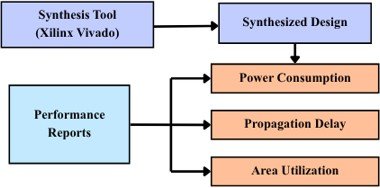

Synthesis by using Vivado

The circuits which are designed have been synthesized by using Vivado software tool in order to achieve gate-level implementations. During the process of synthesis, the reports are being generated which will bring the detailed knowledge on:

-

- Power consumption (static and dynamic)

- Propagation delay (timing analysis)

- Area utilization (LUTs, slices, or gate count)

In calculating the efficiency of digital circuits, these parameters generally called as Power, Performance and Area (PPA) are critical [4]. The synthesis process and parameter extraction are shown in Fig. 2.

Figure 2: Synthesis and Parameter Extraction

Parameter Extraction

After the synthesis process, the key performance parameters are taken from the generated reports.

The reports include the following:

-

- Power serves as the energy consumption in the time of circuit operation

- Delay which shows the speed of computing

- Area which follows the hardware resource usage

Altogether, these parameters form the output variables for machine learning models.

Formation of Datasets

The extracted data which is generated from the synthesis reports is now organized into a structured dataset. Each and every row correlate with one synthesized design. The relationship between input features and output labels used for dataset generation is shown in Table 1.

Input Features | Output Labels |

Adder Type | Power consumption |

Bit-width | Propagation delay |

Area usage |

Table 1: Input Features vs Output Labels for Dataset

Each synthesis run will make a single data sample. By changing the type of adder and bit- widths, large number of datasets are formed. Structured datasets are necessary to train the machine learning models in order to gain correct predictions [5]. This conversion of the hardware outcomes into a data is the main improvement of the proposed approach.

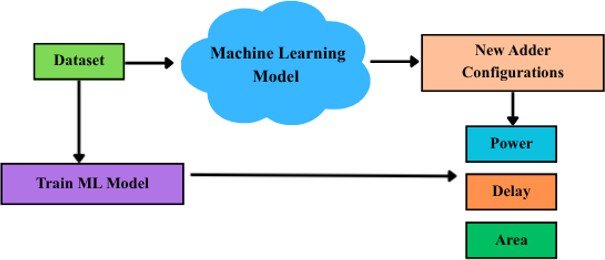

Machine Learning based performance prediction

Machine learning models are trained in order to learn the relation between input features and output labels (performance parameters). The machine learning-based performance prediction model is depicted in Fig. 3.

Linear Regression

Linear regression is used here because it acts as a simple and a baseline model that can capture the relationship between the inputs and the outputs. This model is also efficient for primary level analysis.

Random Forest

Random forest is a model that can build complex and non-linear relationship between the inputs and the outputs. This is a wholesome learning approach that gives high accuracy and strength. This has been mostly used for computation of power and also has identified low prediction fault rates [6].

Machine learning models gradually minimize the need for repeated synthesis by doing the prediction performance directly from the input parameters.

Figure 3: ML based Performance Prediction

Security Analysis on dynamic power behaviour

Along with performance, security is also an important consideration in VLSI systems. Changes in power consumption can lead the circuits to side-channel attacks, where the attackers may take the sensitive information by exploring the power patterns.

This article proposes a structure that integrate security analysis by calculating the dynamic power behaviour:

- Stable consumption of power is considered that the circuit design is more secure.

- Fluctuating power consumption leads to vulnerability which is unsafe to side channel attacks.

Power based side channel vulnerabilities have been studied and they also consider this as a huge challenge in hardware systems [7]. By combining the security analysis and performance, this particular approach gives an overall opinion of the digital adder architecture.

Conclusion

This article addresses a structure that transforms VLSI hardware designs into a machine learning dataset for best and efficient performance prediction and security analysis. By combining it with design, synthesis and data modelling, it minimizes the necessity for repeated synthesis in order to boost the circuit design.

References

- K. Kaul, “Techniques for Optimizing Power, Delay, and Area in VLSI Circuits,” EA Journals, 2025.

- S. Chattopadhyay et al., “Machine Learning Framework for Early PPA Estimation of RTL Designs,” arXiv preprint arXiv:2502.16203, 2025.

- A. Singh et al., “Machine Learning-Based Automation in VLSI Design,” VLSI Journal, 2025.

- M. Zhang et al., “PANDA: Power Estimation Using Hybrid ML Techniques,” arXiv preprint, 2023.

- S. Srivastava et al., “Data Augmentation Techniques for VLSI Machine Learning Models,” arXiv preprint, 2023.

- M. Saqlain et al., “Enhanced Power Estimation of Digital VLSI Circuits Using Machine Learning,” ResearchGate Publication, 2025.

- A. Ain et al., “Security-Aware Adder Design Against Side-Channel Attacks,” IEEE Transactions, 2025.

Cite As

Karlyn FM C, (2026) From Hardware to Dataset: How VLSI Designs Become Machine Learning Data, Insights2Techinfo, pp.1